WARUM TRANSISTOREN IN HF-LEISTUNGSVERSTÄRKERN DURCHBRENNEN

Eine Weißbuch von der Firma AMPLEON

mit Kommentare von Victors R3KR – von der Firma EB104.ru, diese sind kursiv gedruckt.

In den letzten zweieinhalb Jahrzehnten waren VDMOS-Transistoren die Arbeitspferde in vielen ISM- und Broadcast-Anwendungen. Jetzt ist diese Ära aufgrund der kontinuierlichen Verbesserungen der 50-V-LDMOS-Technologie von Ampleon zu Ende.

Die LDMOS-Bauelemente der BLF18x-XR-Serie ermöglichen eine überragende Zuverlässigkeit und niedrigere Systemkosten, während gleichzeitig keine gefährlichen Substanzen mehr erforderlich sind, die mit VDMOS-Paketen verbunden sind. Diese neue XR-Serie wurde speziell für HF-Energieanwendungen in den industriellen, wissenschaftlichen und medizinischen (ISM) Frequenzbändern entwickelt, bei denen Robustheit, Stabilität und Zuverlässigkeit sowohl auf dem Markt als auch beim Transistordesign wichtige Faktoren sind. Die Geräte ermöglichen auch hocheffiziente FM- und VHF-TV-Rundfunksender mit überlegener korrigierbarer Linearität.

Die Kunden von Ampleon haben nun Zugang zu einem Portfolio von Geräten, die alle Designherausforderungen in heutigen Anwendungen auf Basis von Dauerstrich-, gepulsten oder linearen Systemen erfüllen. Dieses Dokument enthält eine detaillierte Beschreibung der Funktionen der Technologie und wie sie mit den erzielten Leistungsverbesserungen zusammenhängen. Anwendungsbeispiele werden mit unseren neuesten 50-V-LDMOS-Bauelementen gegeben, die im Vergleich zu älteren VDMOS und anderen derzeit auf dem Markt erhältlichen 50-V-LDMOS-Technologien eine überlegene Leistung bieten.

Hochspannungs-LDMOS-Technologie

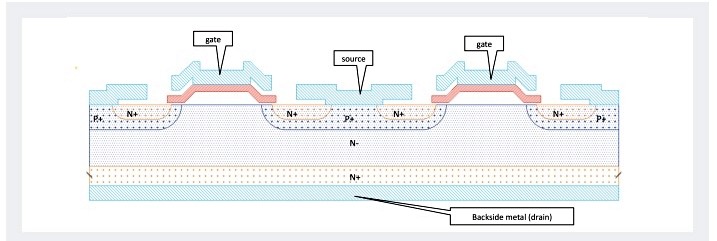

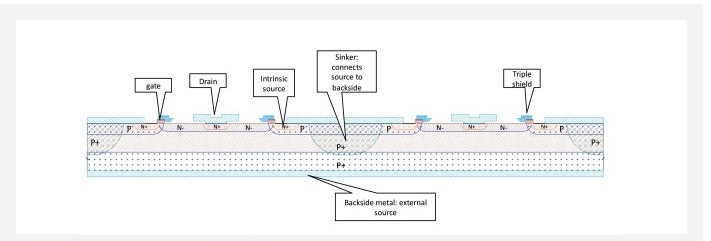

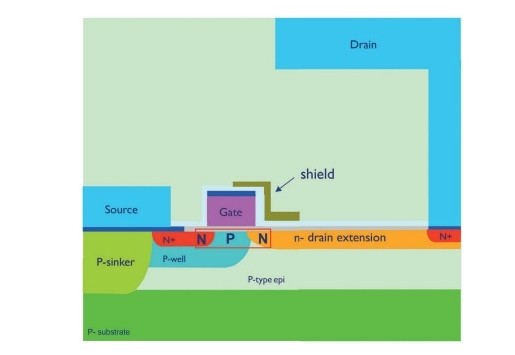

Die extrem robusten 50-V-Transistoren von Ampleon werden in einer 8-Zoll-CMOS-Wafer-Fabrik verarbeitet, die über Lithographiefähigkeiten von bis zu 0,14 μm verfügt. Der LDMOS-Prozess leitet sich vom C075 CMOS-Prozess (0,35 μm Gate) mit LOCOS-Isolierung ab. Zu den Ergänzungen des C075-Prozesses gehören der Quellsenker zum Substrat, die CoSi2-Gate-Silizidierung, der Wolframschild und die pilzartige Abflussstruktur mit dicker, mehrschichtiger AlCu-Metallisierung. Abbildung 1 zeigt einen Querschnitt durch die VDMOS-Technologie, Abbildung 2 zeigt den Querschnitt eines LDMOS-Transistors.

Abbildung 1: Querschnitt durch einen vertikalen DMOS-Sendetransistor. Die Länge des Anschnitts (die Kanallänge) ist die Ebene des Papiers, die Kanalbreite befindet sich in der Ebene des Papiers.

Abbildung 2: Schematischer Querschnitt eines hochmodernen LDMOS-Transistors

Es gibt eine Reihe wichtiger Unterschiede zwischen den Transistoren. Bei einem VDMOS-Transistor fließt der Strom vertikal von oben nach unten, die Rückseite des Chips ist der Drain, und während des Betriebs liegt eine hohe Versorgungsspannung an. Bei einem LDMOS-Transistor fließt der Strom seitlich. Die Quelle ist mit einem P+-Sinker mit der Rückseite des Wafers verbunden, wodurch die Rückseite des Chips zum Source-Anschluss des Transistors wird. Die laterale Konstruktion ermöglicht die Optimierung für den Hochspannungsbetrieb bei HF-Frequenzen durch geeignete Drain-Technik. Die Wahl geeigneter Dotierungsstufen erfolgt in Kombination mit dem Aufbau einer Feldplatte unter Verwendung des „Resurf“-Effekts [1]. Zusätzlich zum Drain Engineering wurde eine Optimierung des parasitären Bipolaren durchgeführt [2], auf die später in diesem Artikel eingegangen wird.

Technologievergleich

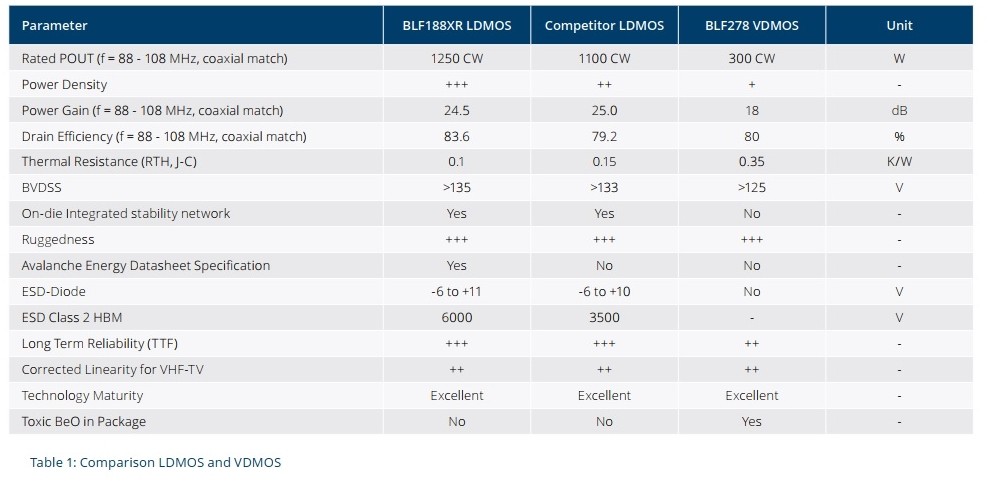

Tabelle 1 zeigt einen Vergleich zwischen VDMOS (BLF278 von Ampleon), dem BLF188XR LDMOS-Transistor von Ampleon und einem Konkurrenzgerät

Im folgenden Absatz wird die Relevanz der verschiedenen Parameter in Tabelle 1 in Bezug auf die verschiedenen Anwendungen erörtert. Wir können zwischen zwei Anwendungsbereichen unterscheiden:

• ISM, hohe bis sehr hohe Leistungspegel, oft anfällig für hohe Fehlanpassungen, bei denen Stabilität, Robustheit und Zuverlässigkeit wichtige Designparameter sind

• Broadcast, hohe bis sehr hohe Spitzenleistungspegel, bei denen Wirkungsgrad und erregerkorrigierte Linearität wichtige Designparameter sind

Wärmewiderstand

Der Wärmewiderstand ist der Schlüsselparameter, der so niedrig wie möglich gehalten werden soll, um:

1. Stellen Sie niedrige Matrizentemperaturen sicher, um eine langfristige Zuverlässigkeit (TTF) zu gewährleisten2

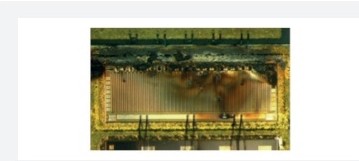

.Maximieren Sie die Verlustleistung, die das Gerät bei Fehlanpassungen bewältigen kann. Hohe Stromverhältnisse und damit eine hohe Verlustleistung können je nach Schaltungsdesign der Anwendung und dem Phasenwinkel der Fehlanpassung auftreten. Dies kann zu sehr hohen Verlustwerten führen, was zu einem thermischen Zusammenbruch des Chips und des Transistors führen kann. Dies führt in der Regel zur vollständigen Zerstörung des Transistors, siehe Abbildung 3.

Abbildung 3: Beispiel für einen Ausfall eines thermischen Bauelements als Folge einer hohen Verlustleistung

Ich gebe ein weiteres Beispiel für eine Berechnung aus dem Artikel:

Zuverlässigkeit

Die mittlere Zeit bis zum Ausfall (MTTF) ist definiert als eine Verringerung der Strombelastbarkeit um 10 % um 50 % der Geräte innerhalb einer bestimmten Stichprobengröße. Der Hauptfaktor für das Versagen des Geräts ist auf die Elektromigration von Metallen auf der Werkzeugoberfläche zurückzuführen.

Bitte beachten Sie, dass die Elektromigration von Metall nicht sofort, sondern im Laufe der Zeit erfolgt. Das heißt, als Sie den Transistor installierten, die Leistung sahen und glücklich waren, aber die Freude möglicherweise nicht lange anhält.

Nachdem die durchschnittlichen Betriebsbedingungen für eine bestimmte Anwendung ermittelt wurden, kann die MTTF anhand des Wärmewiderstandswerts Rth berechnet werden, der im Produktdatenblatt von MRFE6VP61K25H angegeben ist.

Beispiel: Wenn die gewünschte Ausgangsleistung 1100 W bei einem Ölwechselwirkungsgrad von 80 % beträgt.

- IDrain = 1100W / (80% x 50V) ~ 27,5A

- MRFE6VP61K25H Rth = 0,15 °C/W, Gehäusetemperatur = 80 °C

- Verlustleistung = Pdc — Pout + Pin

- Verlustleistung = 50 V x 27,5 A – 1100 W + 4 W = 279 W

- Temperaturanstieg = 279 W x 0,15 °C/W = 42 °C

- TJ = Trise + TC = 42 °C + 80 °C = 122 °C

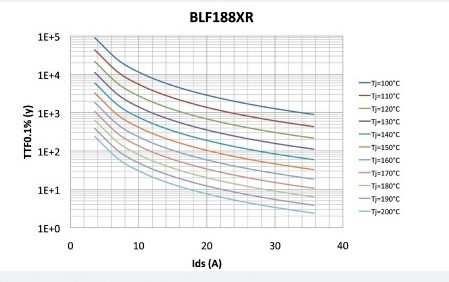

Unter Verwendung von Abbildung 12, die MTTF basierend auf IDrain und TJ berechnet; IDrain = 27,5 A

Bitte beachten Sie, dass die Quarztemperatur in direktem Zusammenhang mit dem Wirkungsgrad des Verstärkers steht. Für mich persönlich wird klar, dass die Temperatur des Kupferradiators unter dem Transistor +65C nicht überschreiten sollte. Von +85C Grad kann keine Rede sein! Bei der Berechnung der Kristalltemperatur können wir die Wärmeübertragung vom Transistorgehäuse zum Kupferkühler nicht berücksichtigen, es scheint mir, dass wir 10-15 Grad hinzufügen müssen, da die Wärmeleitfähigkeit von Lot oder anderen Materialien viel schlechter ist als die von Kupfer.

Beim Löten eines Transistors wird immer Flussmittel verwendet (sonst kann man es nicht verzinnen), das beim Erhitzen siedet, und es bilden sich Hohlräume – sie sind immer da. Nur durch das Löten im Vakuum kann die Kavitätenbildung minimiert werden. In der seriösen Produktion erfolgt die Röntgenkontrolle immer nach dem Einbau des Transistors.

Das Transistorgehäuse kann nicht als Heizkörper betrachtet werden, und selbst der kleinste Hohlraum führt zu einer punktuellen Erwärmung des Kristalls. Wenn einer der Millionen von Transistoren deswegen ausfällt, ist dies der Zusammenbruch des gesamten LDMOS-Bausteins.

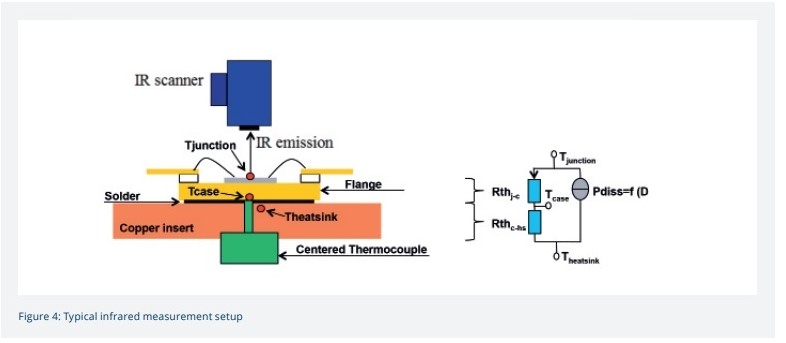

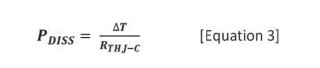

Im Allgemeinen kann der Wärmewiderstand in einen RTH,J-C-Teil (Übergang zum Gehäuse) und einen RTH,C-HS-Teil (Gehäuse zum Kühlkörper) unterteilt werden. Der RTH,J-C wird vom Gerätehersteller spezifiziert und der RTH,C-HS hängt vom verwendeten Materialstapel im Schaltungsdesign ab. Ein typischer Aufbau zur Messung des Wärmewiderstands ist in Abbildung 4 dargestellt.

Abbildung 4: Typischer Aufbau der Infrarot-Messung

Das Setup verfügt über eine Infrarotkamera (IR), die sich direkt über dem Gerät befindet und ein vergrößertes Bild der Sperrschichttemperatur von Abschnitten des Geräts aufnehmen kann. Das Gerät ist auf einen Kupfereinsatz gelötet, der zwischen dem Eingangs- und Ausgangsteil der Prüfschaltung geklemmt wird. Dieses Gesamtsystem wird dann auf eine wassergekühlte Platte gespannt. Um den RTH,J-C zu bestimmen, werden während der Messung die folgenden Informationen gesammelt.

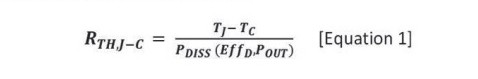

Die Verlustleistung (PDISS) ist eine Funktion der Drain-Effizienz (EffD) und der HF-Ausgangsleistung (POUT). Der Wärmewiderstand eines VDMOS-Transistors ist im Vergleich zu einem LDMOS-Produkt relativ hoch, wie in Tabelle 2 dargestellt.

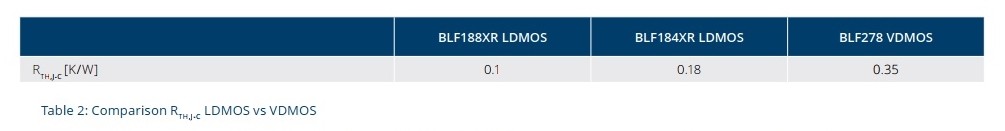

Der relativ hohe RTH,J-C eines VDMOS-Gerätes wird unter anderem dadurch verursacht, dass eine isolierende BeO-Disk benötigt wird, um den VDMOS-Die zu montieren (die Rückseite ist der Drain, der die 50 V Versorgungsspannung führt). Dadurch erhöht sich der RTH,J-C. Auch die Dicke der Matrize spielt eine Rolle für die Gesamt-RTH. Das VDMOS-Werkzeug ist etwa 200 μm dick, da die Werkzeugläpptechniken bei der Entwicklung der Technologie noch nicht so weit fortgeschritten waren. Die LDMOS-Chips, die im Vergleich zu VDMOS auch dünner (120 μm) sind, werden mit einem eutektischen Die-Attach direkt auf den Metallflansch des Transistors montiert. Dadurch entfällt die Notwendigkeit einer thermischen Schnittstelle und somit ein möglichst geringer Wärmewiderstand für LDMOS-Bauelemente. Die Anordnung der aktiven Chip-Bereiche und der Abstand zwischen den Fingern des Chips, wurde für einen optimalen thermischen Widerstand und ein optimales Temperaturprofil entlang des Chips, wie in den in Abbildung 5 gezeigten IR-Ergebnissen untersucht.

Abbildung 5: BLF188XR Infrarot-Temperaturprofil

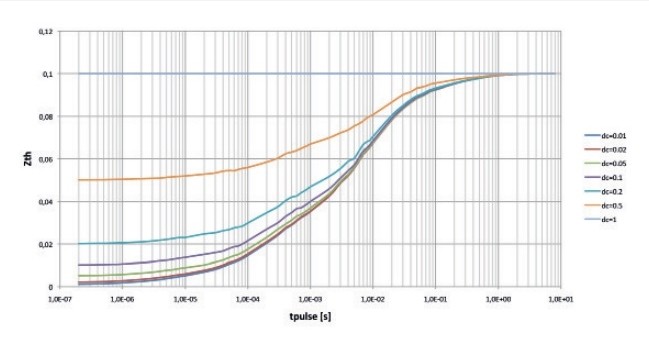

Der thermische Widerstand, manchmal auch als thermische Impedanz (Zth) bezeichnet, eines LDMOS-Transistors ändert sich in Abhängigkeit von der Pulsbreite (tpulse) und dem Tastverhältnis (dc). Diese thermischen Eigenschaften (in Abhängigkeit von der Pulsbreite und dem Tastverhältnis) werden während der IR-Messungen aufgezeichnet. Abbildung 6 zeigt die Ergebnisse für die Änderungen der thermischen Impedanz Zth, wobei dc = 1 dem Dauerstrichbetrieb (CW) entspricht.

Abbildung 6: Thermische Impedanz (Zth) für die BLF188XR in Abhängigkeit von Pulsbreite und Tastverhältnis

Abbildung 7: BLF188XR TTF-Kurven für einen Ausfallanteil von 0,1 % in Abhängigkeit von Gleichstrom und Temperatur

Ein geringer Wärmewiderstand ist wichtig, um die langfristige Zuverlässigkeit des LDMOS-Bausteins zu gewährleisten. Abbildung 7 zeigt die Lebensdauer in Jahren bei einem Ausfallanteil von 0,1 % (TTF0,1 %) für den BLF188XR in Abhängigkeit von der Sperrschichttemperatur und dem Strom-IDS der Ablassquelle (d. h. der Versorgung). TTF0,1% sollte nicht mit MTF50% verwechselt werden, die viel optimistischere Zahlen aufweisen werden.

BVDSS (Vertikale Durchbruchspannung)

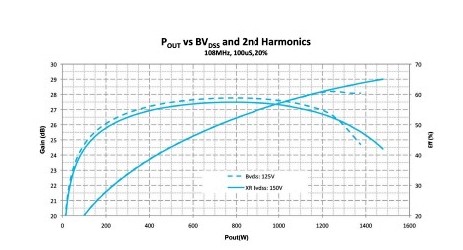

BV DSS ist ein wichtiger Parameter für das Transistordesign und beeinflusst die Leistungsfähigkeit und Robustheit, insbesondere wenn die Wellenform der Ausgangsspannung einen erheblichen Oberschwingungsanteil aufweist. Aus der Theorie ist bekannt, dass die Ausgangsstromwellenform einen signifikanten Gehalt an 2. Harmonischen hat, wenn die interne Stromquelle mit einer Impedanz ungleich Null der 2. Harmonischen abgeschlossen wird. Die resultierende Spannung der 2. Harmonischen trägt zur Grundwellenform bei und begrenzt den Spielraum der Grundausgangsspannung, wodurch die HF-Ausgangsleistung begrenzt wird. Dieser Effekt ist in Abbildung 8 für eine 108-MHz-Testschaltung mit signifikantem Oberschwingungsgehalt dargestellt, d. h. mit nicht optimaler Oberschwingungsterminierung auf Schaltungsebene.

Abbildung 8: Ein höherer BV DSS bei einem hohen Oberschwingungsgehalt verbessert die Ausgangsleistung und den Wirkungsgrad, wenn das Gerät zu komprimieren beginnt

Zwei Transistoren werden verglichen. Der erste hat einen typischen BVDSS von 125 V (gestrichelte Linie) und der andere einen typischen BV DSS von 150 V (durchgezogene Linie). Es ist zu erkennen, dass das Gerät mit der 125 V Durchbruchspannung schneller in die Kompression geht. Die erzielbare Ausgangsleistung ist geringer, und da der Transistor in eine Lawine gerät, wird der Wirkungsgrad auch bei Ausgangsleistungen nahe der Kompression beeinträchtigt. Die Vorteile eines Transistors mit einem hohen BVDSS sind noch größer, wenn der Baustein auf Effizienz abgestimmt ist (hohe Lastleitung), in hohen Betriebsklassen eingesetzt wird oder wenn schwerwiegende Fehlanpassungen angewendet werden. Abhängig vom Anwendungsdesign und in Abhängigkeit vom Phasenwinkel der Fehlanpassung können hohe Spannungsspitzen auf dem Chip auftreten, die zu einer Verschlechterung oder Zerstörung des Transistors führen können. Es liegt auf der Hand, dass bei niedrigeren Betriebsfrequenzen der Effekt von Oberschwingungen höherer Ordnung signifikanter wird und ein hoher BVDSS wichtiger ist. Die BLF18x-Serie hat einen hohen BV DSS, der durch den spezifischen Widerstand und die Dicke der Epi-Schicht bestimmt wird.

Parasitärer bipolarer Zusammenbruch

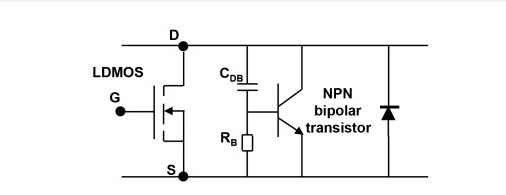

Ein parasitärer NPN-Transistor ist in jedem LDMOS-Transistor als Teil seiner Struktur enthalten. Abbildung 9 zeigt die schematische Darstellung des LDMOS-Transistors, einschließlich des parasitären NPN-Transistors und der Drain-Substrat-Diode. Abbildung 10 zeigt die Position des parasitären bipolaren NPN-Transistors in der LDMOS-Struktur.

Abbildung 9: Elektrische Darstellung des LDMOS und des inhärent vorhandenen parasitären Bipolartransistors und der Drain-Substrat-Diode

Abbildung 10: Parasitärer bipolarer NPN-Transistor in der LDMOS-Struktur hervorgehoben

Die Drain-Source-Diode klemmt die Spannung über das LDMOS und die parasitäre Bipolardiode senkt den überschüssigen Strom auf das Substrat. Bei großen Senkenströmen übersteigt jedoch die Drain-Source-Spannung die Durchbruchspannung der Diode und der parasitäre Bipolartransistor kann ausgelöst werden. Große Senkenströme können durch ein Mismatch-Ereignis, eine unsachgemäße Beendigung von Oberschwingungen oder den Betrieb in der Sättigung verursacht werden. Das Auslösen des parasitären bipolaren Transistors führt zu einem nahezu sofortigen Ausfall des LDMOS-Transistors, ein Beispiel ist in Abbildung 11 dargestellt. Dies zeigt, dass die Fehlersignatur nur ein paar verbrannte Finger zeigt, während Abbildung 3 eine viel größere Zerstörung zeigt, wenn der Transistor in einen thermischen Ausfall gerät.

So können wir durch Öffnen des verbrannten Transistors die Ursache des Fehlers suchen und bestimmen – Überhitzung oder den Betrieb eines parasitären Bipolartransistors.

Abbildung 11: Transistorausfallsignatur, wenn der parasitäre Bipolartransistor getriggert wurde

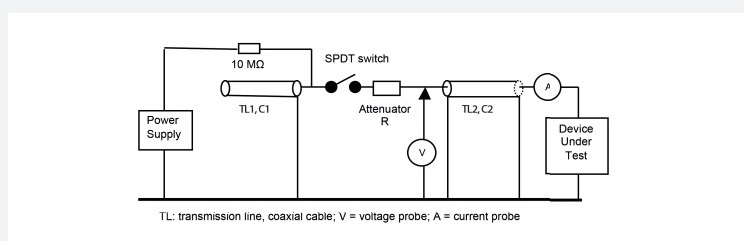

Abbildung 12: Pulsformungsnetzwerk für die TLP-Testmethodik

Um den parasitären Bipolartransistor robuster für ein auslösendes Ereignis zu machen, wurde er durch eine TLP (Transmission Line Pulse) Messung charakterisiert und optimiert. Der TLP-Test ist eine On-Wafer-Charakterisierungsmethode (siehe Abbildung 12) zur Bestimmung der Triggereigenschaften des parasitären Bipolaren im LDMOS-Bauelement. Mit einem kurzen Impuls (50 bis 200 ns) wird die „Snap-Back“-I-U-Charakteristik gemessen. Das Pulsformungsnetzwerk C1-R-C2, bestehend aus TL1, dem Dämpfungsglied TL2 und dem 50-Ohm-Kabel zum Prüfling, wird gewählt, um die gewünschte Impulsanstiegszeit, -dauer und -abfallzeit einzustellen. Die Versorgungsspannung bestimmt die Spitzenprüfspannung, die an das zu prüfende Gerät angelegt wird. Wichtige Parameter, die es zu optimieren gilt, sind der Basiswiderstand RB (siehe Abbildung 9), die Verstärkung und der maximale Basisstrom des parasitären bipolaren NPN-Transistors. Sobald ein LDMOS-Transistor aufgrund eines getriggerten parasitären Bipolars ausfällt, weist das Gerät oft einen niedrigen Gate-Source-Widerstand (< 200 Ohm) auf, wenn es mit einem Ohmmeter am Gate des Geräts gemessen wird. Ein einwandfreies Gerät weist einen sehr hohen Gate-Source-Widerstand (> 1 Megaohm) auf. Eine verbesserte Ablasstechnik in Verbindung mit der Optimierung der Robustheit des parasitären Bipolaren hat zu der extrem robusten 50-V-LDMOS-Technologie von Ampleon geführt.

Wenn Sie also sehen, dass das Gate zum Gehäuse gebrochen ist, dann ist der Transistor nicht wegen des Gates, sondern wegen Überhitzung oder einer großen Anzahl von Oberschwingungen Ihres Verstärkers ausgefallen.

Wenn der Verstärker in die Sättigung eintritt, kommt es zu einer Zunahme der Oberschwingungen, und der Ausgangssignalpegel hört auf zu wachsen oder wächst sehr langsam – dies kann in Niederfrequenzbändern beobachtet werden. Dies ist ein sehr gefährlicher Modus. Viele Verstärker mit Frequenzen von 1,8-3,6 MHz arbeiten einfach ekelhaft und haben einen geringen Wirkungsgrad, was den hohen Pegel der Oberschwingungen bestätigt.

Gefährlich wird es auch, wenn der Verstärker ein ALC-System verwendet, um den Leistungspegel für alle Bänder auszugleichen. Stellen Sie sich vor, Sie stimmen das ALC-System des Transceivers auf 14 MHz ab und sehen eine Ausgangsleistung von 2400 W, gehen dann auf 1,8 MHz und der ALC liefert immer mehr Strom an den Verstärkereingang, um das gleiche Ergebnis zu erzielen – und das kann für diesen speziellen Verstärker unmöglich sein. Dies führt zu einer Sättigung des Transistors, einer Erhöhung der Anzahl der Oberschwingungen und zum Ausfall des Transistors. Nicht unbedingt sofort, aber mit der Zeit wird es definitiv passieren. Ich bin davon überzeugt, dass der Verstärker so ausgelegt werden sollte, dass die Verstärkungsnichtlinearität im gesamten HF-Band nicht mehr als 10% beträgt. Dies ist ein vollständig lösbares Problem, ohne das ALC-System zu verwenden.

On-Die-Stabilitätsnetzwerk

Stabilität und Störleistung sind von besonderer Bedeutung, wenn das Gerät starken Lastfehlanpassungen ausgesetzt ist. Stabilität ist wichtig für ISM-Anwendungen, bei denen strenge Störanforderungen (< -50 dBc) erfüllt werden müssen.

Wenn der Transistor potenziell instabil ist und starken Fehlanpassungsbedingungen ausgesetzt ist, können unechte Produkte auftreten, die über die Spezifikationsgrenze fallen. Die BLF18x-XR-Serie verfügt über On-Die-Stabilitätsnetzwerke, die Stabilitätsprobleme minimieren. Diese internen Netzwerke, zusammen mit einem geeigneten Anwendungsdesign, minimieren die Degradation oder Zerstörung von Transistoren. Die Stabilitätsmaßnahmen, die bei Anwendungsschaltungsdesigns mit der BLF18x-XR-Serie ergriffen werden müssen, sind im Vergleich zu früheren Hochspannungs-LDMOS-Generationen wesentlich geringer und können in einigen Fällen vollständig eliminiert werden. Damit der LDMOS-Transistor dies erreichen kann, wird auf der Gate-Seite des Transistors ein On-Die-RC-Netzwerk integriert, das große Kapazitätswerte von mehreren hundert Pikofarad umfasst. Dieser On-Die-Kondensator wird durch eine MIM-Kappe (Metal-Insulating-Metal-Kondensator) mit Nitrid-Dielektrikum realisiert. Um die Zuverlässigkeit über die gesamte Lebensdauer zu gewährleisten, führt Ampleon ein On-Die-Screening der integrierten MIM-Kappen durch [3]. Ampleon ist das einzige Unternehmen in der Branche, das ein On-Die-Screening für seine extrem robuste LDMOS-Technologie ermöglicht hat, was die Zuverlässigkeit seiner Transistoren weiter erhöht.

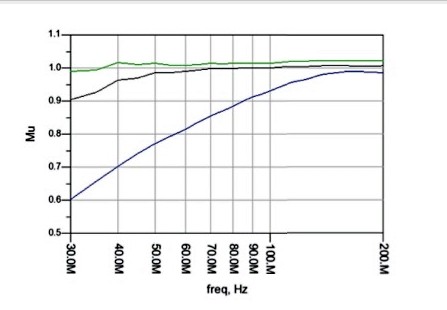

Abbildung 13: Stabilität (Mμ-Faktor) für den BLF188XR (grüne Linie), einen LDMOS-Baustein eines Mitbewerbers (schwarze Linie) und den BLF278 VDMOS-Transistor (blaue Linie)

Abbildung 13 zeigt, dass das BLF188XR bis hinunter zu 40 MHz bedingungslos stabil ist (Mμ > 1), unterhalb von 40 MHz ist das Gerät potentiell instabil. In einem solchen Fall muss möglicherweise eine Stabilitätsmaßnahme auf Schaltungsebene außerhalb des Transistors implementiert werden. Das Wettbewerbsgerät und der BLF278 VDMOS-Transistor weisen einen geringeren Mμ-Faktor als gewünscht auf. Auch das Chip-Layout spielt eine wichtige Rolle für die Gerätestabilität. Ein falsches Chip-Layout kann aufgrund von Schwingungen sogar zu Problemen mit der Leistungsskalierung führen. Ein Transistor mit Stabilitätsproblemen birgt auch das Risiko einer geringeren Robustheit.

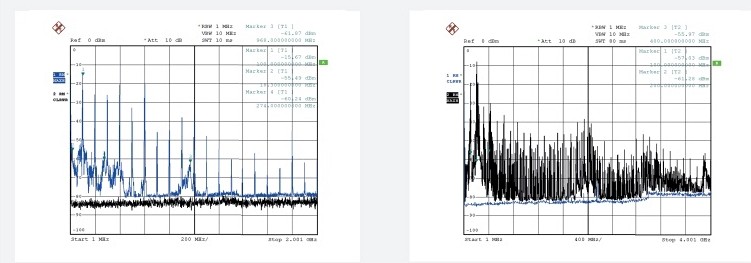

Abbildung 14: Spektraldiagramm des BLF188XR (links) und eines LDMOS-Transistors eines Mitbewerbers (rechts) unter schwierigen Mismatch-Bedingungen

Abbildung 14 zeigt die spektrale Reinheit des BLF188XR im Vergleich zu einem ähnlichen LDMOS-Transistor eines Mitbewerbers unter den gleichen Mismatch-Bedingungen und in derselben Anwendungsschaltung. Im linken Plot (BLF188XR) sind die Störprodukte minimal, es werden lediglich Oberschwingungen angezeigt, die leicht herausgefiltert werden können. Das Diagramm auf der rechten Seite (Konkurrenzgerät) zeigt ein deutlich weniger sauberes Spektrum, ohne die Möglichkeit, die unerwünschten Produkte um den Träger herum herauszufiltern.

Robustheit

Die Robustheit eines HF-Leistungstransistors ist ein komplexes Thema. Wenn ein LDMOS-Transistor starken Fehlanpassungsbedingungen ausgesetzt ist, kann er teilweise beschädigt werden, was zu Leistungseinbußen führen kann, oder im Extremfall kann der Transistor explodieren (siehe Abbildung 3 und Abbildung 11). Die Robustheit des Transistors wird bestimmt durch:

• BV DSS

• Ausfalleigenschaften des parasitären Bipolartransistors

• Verlustleistung, die der Transistor bewältigen kann

• Intrinsische Transistorstabilität (siehe vorheriger Absatz)

• Lawinenenergie, die der Transistor verarbeiten kann

Es gibt zwei Möglichkeiten, die Robustheit eines Transistors zu charakterisieren:

• Ein Test mit hohem VSWR-Wert, bei dem eine Mismatch-Einheit mit einem gepulsten CW-Signal verwendet wird, während die Versorgungsspannung erhöht

wird• VDS, die HF-Ausgangsleistung POUT und die Manipulation der Anstiegs-/Abfallzeit des Impulses

• Bestimmen Sie die Lawinenenergie des Transistors mit einem UIS-Test (Unclamped Inductor Switching)

Test mit hohem VSWR-Wert

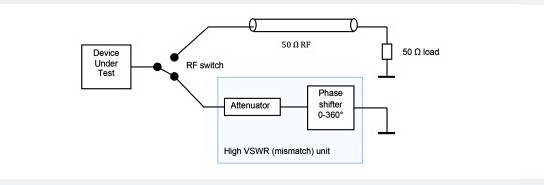

Die Bestimmung der Robustheit des Transistors durch Anwenden einer Fehlanpassung auf die Applikationsschaltung wird durch den Anschluss einer Phaseneinheit an die Testschaltung erreicht.

Abbildung 15: Blockdiagramm-Robustheitsprüfung mit Mismatch-Einheit

Das angelegte VSWR kann reduziert werden, indem ein Abschwächer vor der Phaseneinheit angebracht wird. Das resultierende VSWR wird mit der folgenden Formel berechnet, wobei S das gewünschte VSWR ist.

![]()

Um ein VSWR = 10:1 zu erreichen, beträgt der erforderliche Abschwächer vor dem (idealen) Phasenschieber 0,8715 dB. Bitte beachten Sie, dass es äußerst schwierig ist, eine Phaseneinheit mit einem unendlichen VSWR für alle Phasen zu erstellen. Jeder Verlust in der Phaseneinheit führt zu einer Verringerung des VSWR aus dem Unendlichen. Typischerweise variiert das VSWR einer Phaseneinheit in Abhängigkeit vom Phasenwinkel, und eine gute (praktische) Phaseneinheit hat VSWR-Werte zwischen 65 und 100. Um die Robustheit zu testen, wie sie durch das BVDSS und das parasitäre Bipolar bestimmt wird, wird typischerweise ein gepulstes CW-Signal verwendet. Dadurch wird ein Durchschlag des Transistors bei maximal zulässiger Verlustleistung PDISS vermieden. Die maximale Verlustleistung aufgrund des Erreichens der Verlustleistungsgrenzen kann anhand der maximalen Sperrschichttemperatur (TJ,MAX für die BLF188XR beträgt 225 °C) und des Wärmewiderstands berechnet werden.

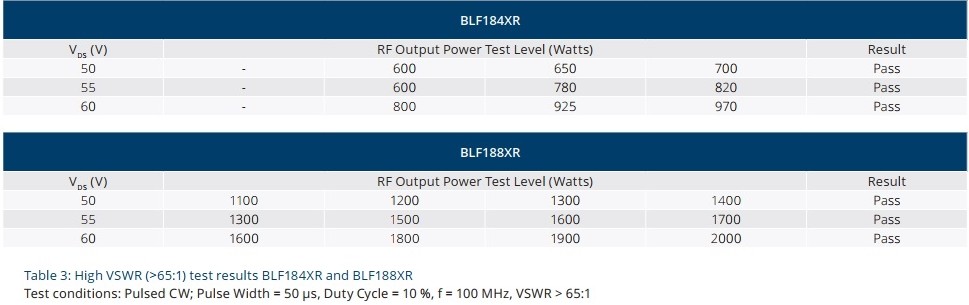

Bei einer Gehäusetemperatur von 75 °C unter CW-Bedingungen beträgt die maximale Verlustleistung 1500 W für eine RTH,J-C von 0,1 K/W. Typische Impulsbedingungen, die bei Ampleon verwendet werden, sind 50 oder 100 μs mit 10 % Einschaltdauer. Schnelle Anstiegs- und Abfallzeiten in Kombination mit hohen Drain-Strömen und hohen Induktivitätswerten in der Applikationsschaltung können sich negativ auf die Robustheit auswirken, da sie hohe Spannungsspitzen erzeugen können, die durch L(dI/dt)-Transienten entstehen. Die Durchbruchspannung der parasitären Bipolarität scheint jedoch für die meisten realen Situationen ausreichend hoch zu sein. Bei Ampleon beginnt die Prüfung der Robustheit mit hohem VSWR bei der nominalen Versorgungsspannung und der nominalen Ausgangsleistung mit einem VSWR-> 65:1 (über alle Phasen). Nachdem die Geräte diesen Test bestanden haben, wird der Eingangsantrieb schrittweise auf ein Niveau erhöht, bei dem das Gerät eine Kompression von 5 dB hat. Sobald dieser Test bestanden ist, wird er wiederholt, aber jetzt mit erhöhter Versorgungsspannung. Tabelle 3 zeigt die Prüfergebnisse für die BLF184XR und BLF188XR für Versorgungsspannungen (VDS) bis 60 V.

UIS-Test zur Bestimmung der Robustheit

Der UIS-Test wurde entwickelt, um die Lawinenzuverlässigkeit von Schaltnetzteil-MOSFETs zu testen. Leistungs-MOSFET-Bauelemente sind für eine bestimmte maximale BV DSS-Sperrspannung ausgelegt, und der Betrieb von Bauelementen bei VDS weit über der BVDSS-Durchbruchschwelle führt zur Bildung und Vermehrung von Elektron-Loch-Paaren. Dieser Reverse-Avalanche-Strom fließt durch die pn-Diode des Drain-Substrats und verursacht eine hohe Verlustleistung, die zu einer thermischen Zerstörung führt. Der UIS-Test bestimmt EAS, die Menge an Lawinenenergie, die das Gerät in der pn-Diodenstruktur ableiten und absorbieren kann. Der UIS-Test wird nicht mit dem Gerät unter nominalen Bias-Bedingungen durchgeführt.

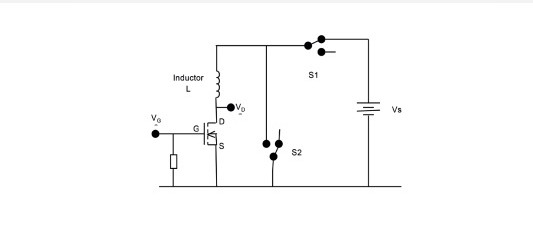

Abbildung 16: Schematische Darstellung des Prüfaufbaus für ungespanntes induktives Schalten (UIS)

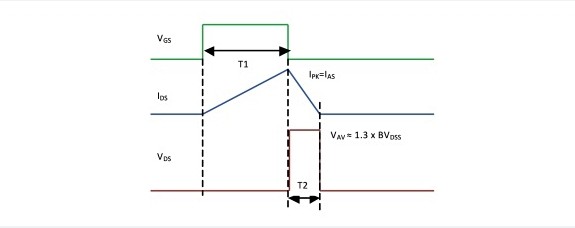

Ein vereinfachtes Schema des UIS-Testers ist in Abbildung 16 dargestellt. Zu Beginn des Tests wird der Schalter S1 geschlossen und das Gate des Prüflings mit einem VGS = 10 V (Gerät vollständig geöffnet) bestromt. Der Drainstrom steigt linear an (T1-Periode, siehe Abbildung 17). Der Momentanstrom wird mit einer Breitband-Stromzange gemessen (nicht im Diagramm dargestellt). Wenn der Drain-Strom den programmierten maximalen Spitzenstrom erreicht, wird der Prüfling abgeschaltet, indem die Gate-Spannung auf 0 V abgesenkt wird und S1 öffnet, die Drain-Leistung entfernt und S2 geschlossen wird. Der Strom in der Induktivität fließt weiter und lässt die Spannung am Prüfling ansteigen, bis die Lawinendurchbruchspannung erreicht ist. Das Gerät beginnt in einer Lawine zu leiten und leitet die im Induktor gespeicherte Energie ab. Wenn das Gerät mit der Verlustleistung umgehen kann, fällt der Strom linear ab (T2-Periode, siehe Abbildung 17), bis die Energie vollständig erschöpft ist.

Abbildung 17: Zeitdiagramm des LawinendurchbruchstestsT1 zeigt die Ladung der Induktivität. T2 stellt die Lawinenphase dar

Danach wird der Induktorwert L auf einen höheren Wert erhöht und der Vorgang so lange wiederholt, bis die Lawinenspannung VAV während der T2-Periode zusammenbricht. Nach diesem Ereignis wird der Test gestoppt. Nun kann die applizierte Energie und damit die absorbierte Einzelpuls-Lawinenenergie EAS berechnet werden (Gleichung 4) für den gewählten maximalen Prüfstrom IAS.

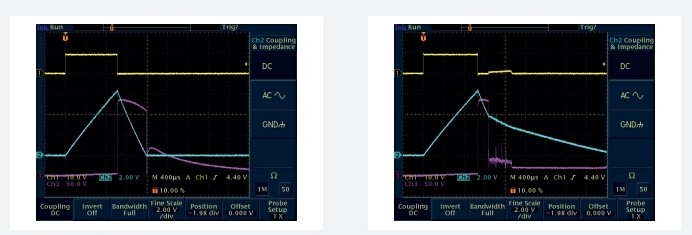

Abbildung 18 zeigt die Avalanche-Wellenformen für die BLF184XR bei einem Lawinenstrom von 25 A. Das linke Bild zeigt den letzten Test vor dem Lawinenzusammenbruch. Das rechte Bild zeigt den Lawinenzusammenbruch während T2.

Abbildung 18: BLF184XR Lawinenwellenformen kurz vor und während des Lawinendurchbruchs

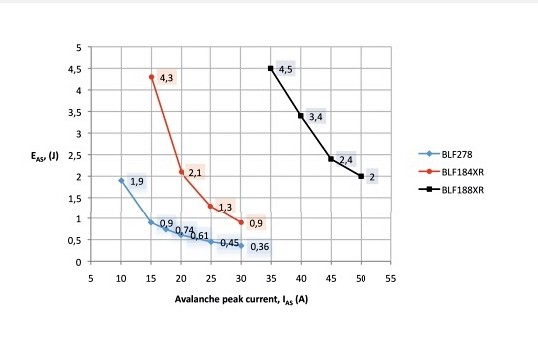

Eine Zusammenfassung der Lawinentestergebnisse mit dem UIS-Tester, durchgeführt am BLF278 (VDMOS) und BLF184XR und BLF188XR, ist in Abbildung 19 zu finden. Beachten Sie, dass die folgenden Abbildungen für einen einzelnen Abschnitt dieser Push-Pull-Transistoren gelten.

Abbildung 19: Avalanche-Testergebnisse für den BLF278, BLF184XR und BLF188XR für einen einzelnen Transistorabschnitt

ESD-Diodenverbesserung

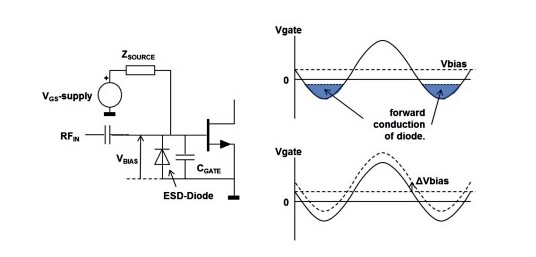

VDMOS-Geräte verfügten über keinen ESD-Diodenschutz auf der Gate-Seite des Transistors. Ältere 50-V-LDMOS-Bauelemente wie der BLF178P verwendeten eine einseitige ESD-Diode zum Schutz vor ESD-Ereignissen auf dem Gate. Diese einseitige ESD-Diode hatte eine Spezifikation von -0,5 bis +11 V. Abhängig von der Anwendung und dem Design der Anwendungsschaltung ist es möglich, dass die einseitige ESD-Diode beginnt, zu leiten, wenn der negative Zyklus der HF-Wellenform -0,5 V überschreitet (siehe Abbildung 20).

Abbildung 20: Einseitige ESD-Diode kann zu Verschiebungen in VBIAS führen

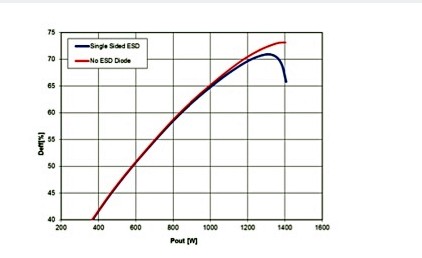

Der Grad der Gleichrichtung wird durch die Geschwindigkeit und Dauer des Signals bestimmt (gepulste Signale und digital modulierte Signale haben einen geringeren Einfluss als CW-Signale). Sie wird auch durch die Quellenimpedanz (ZSOURCE) der Gate-Bias-Schaltung (VGS-Versorgung) bestimmt. Eine hohe Quellenimpedanz führt zu mehr Δ VBIAS (siehe Abbildung 20). Eine Änderung des VBIAS bewirkt eine Verschiebung des Arbeitspunktes des Transistors und kann die Betriebsart von Klasse-C auf Klasse-AB oder noch schwerwiegender auf Klasse-A-Betrieb ändern. Abbildung 21 zeigt die Verschlechterung des Wirkungsgrads bei hohen Kompressionsstufen für ein Produkt ohne ESD-Diode und ein Produkt mit einer einseitigen ESD-Diode.

Abbildung 21: Verschlechterung der Drain-Effizienz als Folge einer VBIAS-Verschiebung, wenn die einseitige ESD-Diode vorhanden ist. Wenn keine ESD-Diode vorhanden ist, tritt keine VBIAS-Verschiebung auf (keine Gleichrichtung)

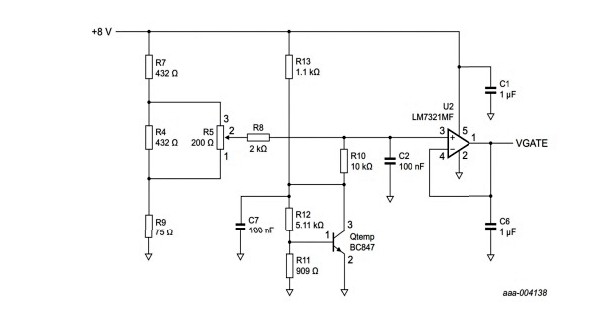

Es wird immer empfohlen, eine niedrige ZQUELLE für die VGS-Versorgung zu haben. Ampleon verwendet in der Regel eine Schaltung mit einer niedrigen Quellenimpedanz. Das schematische Diagramm dieser Schaltung ist in Abbildung 22 zu finden. Eine detaillierte Beschreibung dieser VGS-Versorgungsschaltung finden Sie in [4].

Abbildung 22: Niedrige ZSOURCE-Gate-Bias-Schaltung

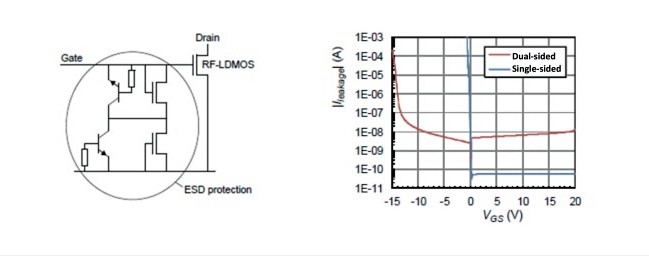

Die Serien BLF17x-XR und BLF18x-XR verwenden eine „beidseitige“ ESD-Diodenstruktur (siehe Abbildung 23) mit Grenzwerten von -6 bis +11 V. Links die schematische Darstellung der implementierten ESD-Struktur, rechts die Ableitströme sowohl für die einseitige als auch für die beidseitige ESD-Diode in Abhängigkeit von VGS. Durch die beidseitige ESD-Diode eignet sich der Transistor besser für Anwendungen, die in Class-C arbeiten, und für Anwendungen, bei denen der Transistor tief in der Sättigung betrieben wird. Im Falle einer doppelseitigen ESD-Diode findet keine Gleichrichtung statt, und der VBIAS bleibt unter härtesten Bedingungen konstant.

Abbildung 23: Schematische Darstellung der in der Serie BLF18x-XR implementierten ESD-Diode und Ableitverhalten der ein- und beidseitigen ESD-Diode

Die BLF18x-XR-Transistorfamilie ist ideal für lineare Anwendungen, wobei das interne Chip-Layout für den linearen Betrieb verbessert wurde. Abbildung 24 zeigt die unkorrigierte Linearität für ein DVB-T-Signal bei 225 MHz. Auf der linken Seite ist die Leistung für eine frühere Hochspannungs-LDMOS-Generation dargestellt. Auf der rechten Seite ist die unkorrigierte DVB-T-Schulterleistung für die BLF18x-XR-Serie dargestellt. Es wurden Verbesserungen bei niedrigeren Leistungen erzielt, was eine einfache Vorkorrektur des Transistors ermöglicht.

Abbildung 24: Der BLF188XR (rechts) eignet sich hervorragend für lineare Anwendungen. Auf der linken Seite eine ältere LDMOS-Generation, die eine geringere Linearität bei niedrigeren Leistungspegeln aufweist, was schwieriger zu korrigieren sein kann

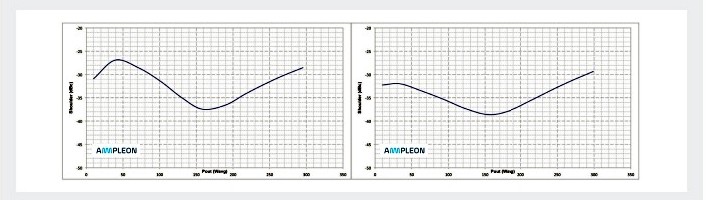

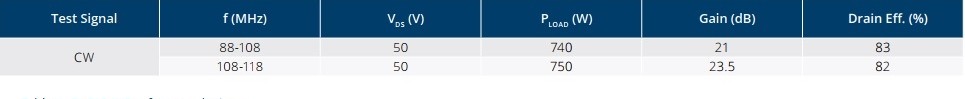

Referenzdesigns und Anwendungshighlights der BLF18x-XR-Serie

Zur Unterstützung von Design-In-Aktivitäten wurde eine Vielzahl von Referenzdesigns erstellt. Die Tabellen 4 und 5 geben einen Überblick über die Designs, die derzeit für die BLF184XR bzw. BLF188XR verfügbar sind. Vier BLF188XR Referenzdesigns werden näher erläutert. Umfangreiche Testberichte einschließlich Stückliste, Leiterplatten-Layoutdateien und Grundplattenzeichnungen sind verfügbar.

Tabelle 4: BLF184XR Referenzdesigns

Schlussfolgerung.

Achten Sie auf die typischen Verstärkerdesigns, die von Transistorherstellern in ihren Datenblättern angeboten werden. Sie alle haben einen hohen Wirkungsgrad, im Durchschnitt etwa 80%. Damit Ihr Verstärker zuverlässig ist, müssen Sie sich darum bemühen. Ein hoher Wirkungsgrad ist der allererste und wichtigste Parameter, auf den Sie achten müssen, die Lebensdauer des Transistors hängt davon ab.

Ich werde einige Gedanken zum Thema des Addierens von Kräften bei HF hinzufügen.

Bei der Verwendung moderner Transistoren ist das Addieren von Leistungen bis zu 2 kW sinnlos und schädlich. Ich werde dies am Beispiel von zwei Kilowatt erklären, die addiert werden, um 2 Kilowatt zu erreichen. Jeder Verstärker verwendet einen 9:1-Transformator und einen Balun. All dies wird dem Addierer zugeführt. Wenn wir die Leistungen addieren, erhalten wir einen Widerstand von 25 Ohm, dann erhalten wir mit einem 2:1-Transformator den Widerstand, den wir von 50 Ohm benötigen. Im Volumen dieses Verstärkers haben wir also zwei 9:1-Transformatoren, zwei Baluns, einen Combiner und einen 2:1-Transformator. Eine große Anzahl von Ferriten. Die größten Verluste bekommen wir beim 2:1 Transformator, da ein solcher Transformator ein sehr kompromissloses Gerät mit geringem Wirkungsgrad ist. Ein Verstärker mit einer solchen Schaltungslösung ist offensichtlich zu einem geringen Wirkungsgrad verdammt. Und wenn wir Signale mit einem hohen Oberschwingungsanteil hinzufügen, addiert sich auch deren Pegel, wächst und die Anzahl der Oberschwingungen nimmt zu. Glauben Sie mir, ich habe solche Verstärker gebaut.

Viele werden mir widersprechen und versichern, dass das Addieren von Leistungen auf UKW ganz normal ist. Bei hohen Frequenzen haben Verstärker einen geringen Oberschwingungspegel am Ausgang, da Resonanztransformatoren verwendet werden und Transistoren unter Berücksichtigung der oberen Betriebsfrequenz ausgewählt werden, daher werden bei solchen Verstärkern Oberschwingungen auf einen Pegel von -20-30 dB unterdrückt. Die Addition reiner Signale erfolgt mit einem hocheffizienten Resonanzaddierer mit minimalen Verlusten.

Für das HF-Band ist es viel einfacher, Transistoren parallel zu schalten, wie es EW3MM und viele andere Funkamateure in ihren Designs getan haben. Wenn Sie zwei 4:1-Transformatoren in Reihe am Ausgang von parallel installierten Transistoren installieren, erhalten Sie eine 16:1-Transformation und eine Ausgangsleistung von 2000 W. Der 4:1-Transformator hat unter anderen Transformatoren die geringstmöglichen realisierbaren Verluste. Wenn Transistoren parallel geschaltet werden, verringern sich ihre obere Betriebsfrequenz und ihr Oberschwingungspegel. Was sich positiv auf die Effizienz auswirkt.

Die Hauptsache ist, die Kühlung nicht mit irgendwelchen Tricks zu verbessern – kleine Kühler, die auf Transformatoren, Flüssigkeiten und dergleichen blasen (all dies hat keinen Einfluss auf den Oberschwingungspegel und der Verstärker wird nicht zuverlässiger!), die Hauptsache ist, einen hohen Wirkungsgrad zu erreichen.

Die Übersetzung der Kommentare erfolgte maschinell, im Original und ohne meine Kommentare (fett kursiv im Text) ist unter den Links zu lesen:

https://www.ampleon.com/documents/white-paper/AMP-WP-2017-0329.pdf

Guter Artikel aber als kleine Anmerkung – 80% Wirkungsgrad erreicht man bei Sättigungsbetrieb also z.B. FM wie beim Rundfunk.

Bei SSB Betrieb im Linearbereich gibt es keine 80% Wirkungsgrad dort liegt er bei ca. 55%. Im übrigen werden die hohen Wirkungsgrade in den Datenblättern bei Pulsbetrieb gemessen und angegeben – das hat mit dem realen Betrieb im Amateurfunk nichts zu tun.

Viele Verstärker Datenblätter insbesondere solche im Internet übernehmen einfach die Wirkungsgrade aus den Datenblättern der Hersteller…….

73,Edwin – DC9OE