STEMlab 16 mit externer Clock nutzen, Teil II von Edwin DC9OE

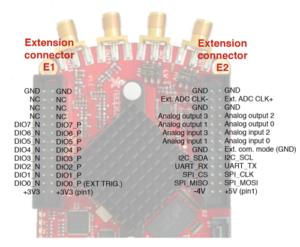

Bei dieser SDRlab-Version handelt es sich um den Standard STEMlab 122-16, der so modifiziert wurde, dass der ADC- und DAC-Takt von einer externen Taktquelle geliefert werden kann. Der externe Takt sollte an die Ext ADC CLK- und + Pins angeschlossen werden. Die externen Taktsignalpegel sollten LVDS im Bereich von 1MHz bis 122,8MHz gemäß ADC-Spezifikation sein.

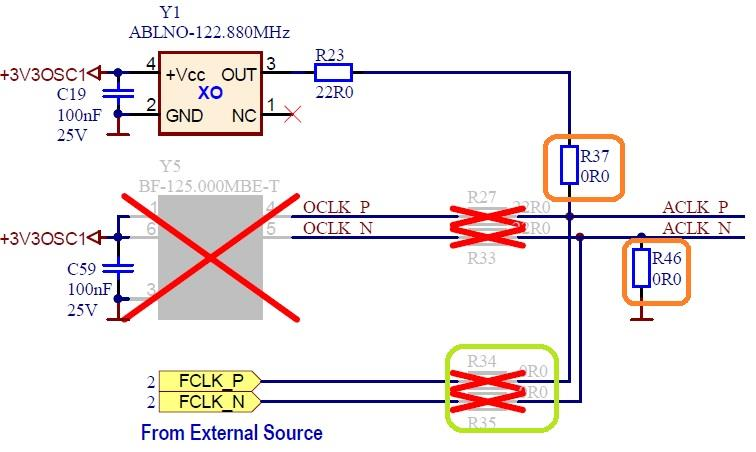

ADC clock can be provided by:

- On board 122.88MHz XO (default)

- From external source / through extension connector (instructions provided bellow)

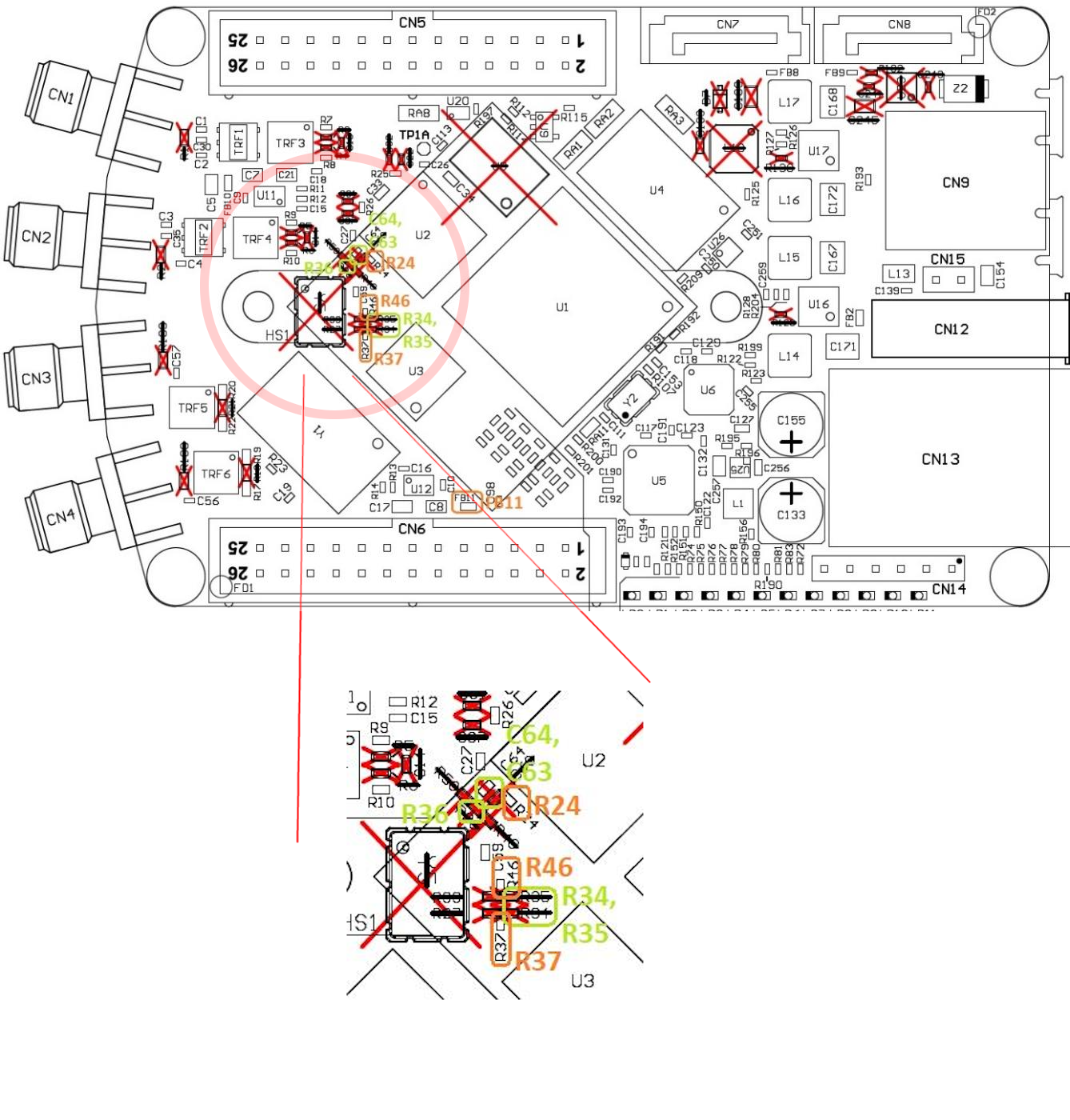

- Remove: R37, R46

- Add: R34 = 0R, R35 = 0R

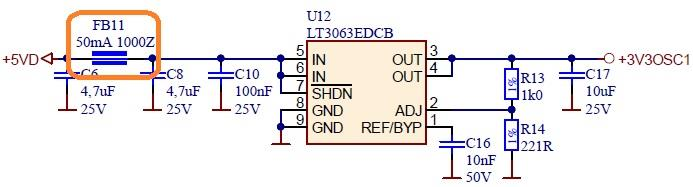

- Remove: FB11

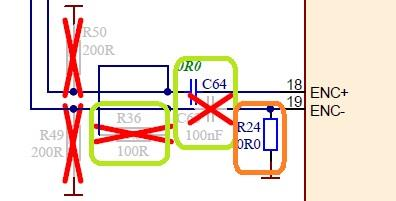

- Remove: 0R on C64, R24

- Add: C64 = 100nF, C63 = 100nF, R36 = 100R

Hallo OM’s

vor einiger Zeit hatte ich angekündigt ein paar Erfahrungen zum Thema STEMlab 16 mit externer Clock abzugeben.

Da diese Version doch einiges an Aufpreis kostet stellt sich zunächst die Frage ist die Sache den Spass wert….

Die notwendigen Umbauarbeiten sind eigentlich überschaubar, aber was uns und vermutlich viele andere bisher aufgehalten hat ist die doch extrem kleine und enge Bauform der Komponenten auf dem Board.

Es geht in jedem Fall nur unter dem Mikroskop – Details der notwendigen Änderungen finden sich hier

https://redpitaya.com/rtd-iframe/?ifram … dware.html

Wie dem auch sei, eine nächste Hürde die sich ergibt ist die Ansteuerung des Boards mit dem Oszillatorsignal , Red Pitaya schreibt ganz lapidar, dass man ein LVDS Signal nutzen soll….. nicht sehr hilfreich…

Beim Studium des Datenblattes von Analog Devices stellt man fest dass es auch einen Vorschlag für die Einspeisung eines Sinus Signals mit Trafo gibt.

Diese Variante habe ich nun als Basis genutzt und einen eigenen Trafo angeschlossen.

Eine genaue Analyse der Umbauanleitung von Red Pitaya ergibt, dass die beiden Trennkondensatoren und der 100Ohm Widerstand schon auf dem Board vorhanden sind.

daher sollte es ausreichend sein lediglich einen Trafo anzuschliessen der das Signal symmetriert.

Der Trafo wurde auf einem Miniatur-Doppellochkern von Würth erstellt, als Draht habe ich Fädeldraht verwendet.

Erste Tests waren recht erfolgreich, der ADC funktioniert ab einem Pegel von -20dBm und ich konnte bis zu einem Pegel von 0dBm keinen Unterschied im Empfangssignal feststellen, denke also das ein Pegel von -10dBm +/- 3dBm ganz passend sein sollte.

Höhere Pegel habe ich nicht getestet weil ich den ADC nicht gefährden wollte.

Was versprechen wir uns nun davon ???

– eine externe Clock kann rauschärmer ausgeführt werden

– die auf dem Board befindliche Clock wird vom Kühlkörper des FPGA aufgeheizt das ist suboptimal

– wir planen die Möglichkeit einer GPS Synchronisation der Clock

Ich hoffe die Info ist für den einen oder anderen nützlich.

73,Edwin – DC9OE

Ich habe mich heute mit dem TX Signal beschäftigt und dabei festgestellt dass es zu Jitter Effekten kommt (Signal springt um ein paar Hz).

Das Problem verschwindet oberhalb 0dBm und ich habe bis +10dBm getestet.

Habe dann +6dBm als gut funktionierenden Pegel festgelegt.Anbei ein Screenshot eines recht hoch aufgelösten und stabilen Signals ( Clock war allerdings auch ein GPS stabilisierter R&S SML03….)

Ein kleines Problem gibt es noch mit zwei Signalen in jewei9ls ca. 170KHz , die sind allerdings mit externer clock auch unkritischer bei -60dBc.

Ich nehme an das diese Höcker vom Schaltnetzteil kommen.

Soweit der kleine Update.

73,Edwin – DC9OE

- Dateianhänge

-

… vielleicht auch noch interessant für den einen oder anderen, mich haben die erzielbaren TX IMD Werte des STEMlab16 mit externer Clock interessiert:

-90dBc oberhalb des Doppeltons unterhalb mit den vorhandenen Möglichkeiten nicht messbar.

(Equipment R&S FSU8)

Messfrequent 7,2MHz / Output ca. +3dBm PEP

73,Edwin – DC9OE